锁相的意义是相位同步的自动控制,能够完成两个电信号相位同步的自动控制闭环系统叫做锁相环,简称PLL。它广泛应用于广播通信、频率合成、自动控制及时钟同步等技术领域。

一个典型的锁相环(PLL)系统,是由鉴相器(PD),压控荡器(VCO)和低通滤波器(LPF)三个基本电路组成,如图1,

图1

一.鉴相器(PD)

构成鉴相器的电路形式很多,这里仅介绍实验中用到的两种鉴相器。

1.异或门鉴相器 异或门的逻辑真值表示于表1,图2是逻辑符号图。

|

|||||||||||||||||||

|

图2 |

表1 | ||||||||||||||||||

从表1可知,如果输入端A和B分别送入占空比为50%的信号波形, 则当两者存在相位差Dθ时,输出端F的波形的占空比与Δθ有关,见图3。将F输出波形通过积分器平滑,则积分器输出波形的平均值,它同样与Δθ有关,这样,我们就可以利用异或门来进行相位到电压的转换,构成相位检出电路。于是经积分器积分后的平均值(直流分量)为:

U = Vdd * Δ θ/π (1)

不同的Δθ,有不同的直流分量Vd。Δθ与V的关系可用图4来描述。从图中可知,两者呈简单线形关系:

Ud = Kd *Δθ (2)

Kd 为鉴相灵敏度

图3 图4

2.边沿触发鉴相器 前已述及,异或门相位比较器在使用时要求两个作比较的信号必须是占空比为50%的波形,这就给应用带来了一些不便。而边沿触发鉴相器是通过比较两输入信号的上跳边沿(或下跳边沿)来对信号进行鉴相,对输入信号的占空比不作要求。

二.压控振荡器(VCO)

压控振荡器是振荡频率ω0受控制电压UF(t)控制的振荡器,即是一种电压——频率变换器。VCO的特性可以用瞬时频率ω0(t)与控制电压UF(t)之间的关系曲线来表示。未加控制电压时(但不能认为就是控制直流电压为0,因控制端电压应是直流电压和控制电压的叠加),VCO的振荡频率,称为自由振荡频率ωom,或中心频率,在VCO线性控制范围内,其瞬时角频率可表示为:

ωo(t)= ωom + K0 UF(t)

式中,K0——VCO控制特性曲线的斜率,常称为VCO的控制灵敏度,或称压控灵敏度。

三.环路滤波器

这里仅讨论无源比例积分滤波器如图5。其传递函数为:

式中:τ1 = R1 C

τ2 = R2 C

图5

四.锁相环的相位模型及传输函数

图6

图6为锁相环的相位模型。要注意一点,锁相环是一个相位反馈系统,在环路中流通的是相位,而不是电压。因此研究锁相环的相位模型就可得环路的完整性能。

由图6可知:

(1)当A点断开环路时,锁相环的开环相位传输函数为

KL(S)=

(2)环路闭合时的相位传输函数为

H(S)

(3)环路闭合时的相位误差传输函数为

He(S)=

当环路滤波器选用无源比例积分滤波器时,经推导可得:

H(S)=

式中,,τ1 = R1 C ,τ2 = R2 C

2x

x= , K = Kd Ko

同样可得:

He(S)=

ωn称为系统的固有频率或自然角频率;

x 称为系统的阻尼系数。

要注意的是上面讨论中的ω指的是输入信号相位的变化角频率,而不是输入信号本身的角频率。如输入信号是调频信号,则ω指的是调制信号的角频率而不是载波的角频率。

五.锁相环的同步与捕捉

锁相环的输出频率(或VCO的频率)ωo能跟踪输入频率ωi的工作状态,称为同步状态,在同步状态下,始终有ωo = ωi。在锁相环保持同步的条件下,输入频率ωi的最大变化范围,称为同步带宽,用DωH 表示。超出此范围,环路则失锁。

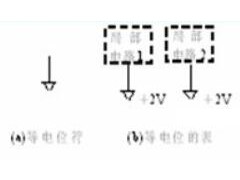

失锁时,ωo≠ωi,如果从两个方向设法改变ωi,使ωi向ωo靠拢,进而使Δωo =(ωi-ωo)↓,当Δωo小到某一数值时,环路则从失锁进入锁定状态。这个使PLL经过频率牵引最终导致入锁的频率范围称为捕捉带Δωp。同步带ΔωH,捕捉带Δωp 和VCO 中心频率ωo的 关系如图7。

图7